咨询电话: 13704000378

又一巨头发力先进封装!

发布于 2025-08-17 02:14 阅读()

近日,三星电子与特斯拉签下165亿美元芯片代工大单,这一合作不仅瞬间提振了三星的市场信心,更在其晶圆代工业务长期低迷的现状下,撕开了一道曙光。

长期以来,三星在晶圆代工领域的发展可谓屡遇波折。在先进制程技术的角逐中,尽管三星率先在3纳米工艺采用GAA全环绕栅极技术,试图弯道超车台积电,却因初期良率问题陷入被动。市场研究机构估算,三星制造3纳米芯片的成本较台积电高出约40%,导致高端客户订单流失,苹果、英伟达等行业巨头持续向台积电靠拢。据TrendForce数据,2025年第一季度,台积电全球代工市场份额高达67.6%,三星却从上个季度的8.1%下滑至7.7%。

在制程推进上,三星原计划2027年量产的1.4纳米工艺,于2025年6月宣布推迟至2029年,测试线建设同步暂缓。同时,德州泰勒市尖端制程晶圆厂因客户匮乏,开业时间延迟至2026年,进一步凸显其在先进制程市场拓展的艰难。

然而,先进制程攻坚的压力下,三星已悄然将目光投向另一关键战场。近年来,先进封装已成为半导体行业的战略高地,面对晶圆代工的结构性挑战,这家科技巨头选择以加码先进封装技术作为突围路径,一系列新动作正陆续展开,为其在半导体竞争中开辟着新的可能性。

在与特斯拉签署价值165亿美元的芯片代工大单后,三星迅速抛出一记重磅战略举措。近日,三星正式官宣,计划豪掷70亿美元在美国打造一座先进芯片封装工厂。这一消息瞬间点燃行业关注热情,成为全球半导体领域热议焦点。

上文提到,三星晶圆代工业务长期以来深陷泥沼。而特斯拉的巨额订单,犹如久旱逢甘霖,极大提升了三星的市值与市场信心,也为其后续投资计划注入了强心针,坚定了三星在美国市场进一步深耕布局的决心。

从规划来看,这座先进封装工厂选址美国,精准锚定美国半导体产业当前的薄弱环节。当下,美国在芯片设计与晶圆制造环节实力强劲,拥有英伟达、高通等设计巨头,台积电、英特尔也在当地设有晶圆厂,但高端封装技术却严重滞后,本土尚未建成高端封装设施。全球90%的先进封装产能集中在亚洲,美国本土缺乏2.5D/3D堆叠、Chiplet集成等关键技术设施。这一产业洼地成为三星战略切入的核心靶点。

这座70亿美元的封装工厂将成为三星“设计-制造-封装”一体化模式的关键环节。根据规划,工厂将聚焦高端封装技术,与德州泰勒晶圆厂形成协同,为客户提供从芯片设计到成品交付的全流程服务。这一布局精准卡位台积电的时间差——台积电美国先进封装厂最快2029年才能投产,三星若能率先落地,便能抢占宝贵的市场先发优势,在时间窗口上赢得先机。

值得注意的是,三星的投资节奏与订单获取形成联动。在拿下特斯拉订单十天后,其又斩获苹果图像传感器订单,显示出客户对其本土化产能的迫切需求。为规避美国关税壁垒,从芯片制造到封装测试的全流程本地化已成为必然选择,这进一步凸显了建设本土封装厂的紧迫性。

此外,从技术卡位角度而言,随着半导体技术演进,先进封装成为提升芯片性能、实现异构集成的关键路径。三星在先进封装领域的扩展计划剑指台积电凭借CoWoS技术占据的AI芯片封装主导地位。同时,在Chiplet生态构建上,三星通过将HBM高带宽内存与逻辑芯片高效协同封装,有望联合美国芯片设计企业,打造下一代Chiplet生态,在未来芯片技术竞争中占据有利位置。

再考虑到供应链布局角度,在美国本土建立封装产能,契合全球供应链本地化、安全化趋势。三星可依托德州泰勒晶圆厂,为客户提供从芯片设计、制造到封装的一站式服务,大幅缩短交付周期,提升对客户需求的响应速度。尤其在AI芯片需求井喷的当下,美国本土封装产能的补充,将为英伟达、AMD等高性能计算芯片企业提供更便捷、高效的供应链选择,增强三星在高端芯片市场的综合竞争力。

政策红利同样不可忽视。美国《芯片与科学法案》提供的520亿美元补贴中,25亿美元专门投向先进封装领域。三星的投资计划与政策导向高度契合,有望获得可观补贴支持,有效降低初期投资风险。

不过,三星这一布局并非坦途。美国建厂面临人力、能源成本高昂难题,较韩国高出30%-40%,如何平衡成本成为挑战。此外,美国半导体专业人才,特别是先进封装领域技术骨干存在缺口,三星需妥善解决人才招募与培养问题,才能确保工厂顺利运营。

总而言之,三星70亿美元的美国封装厂投资,既是对市场空白的精准卡位,也是其半导体业务战略转型的关键落子。通过填补美国产业链短板、整合政策资源、发挥一体化优势,三星正试图在先进封装领域实现对台积电的弯道超车。这场布局的最终成效,不仅将影响三星自身的市场地位,更将重塑全球半导体产业的竞争格局。

近日,据行业消息人士透露,三星计划投资250亿日元(约合1.7亿美元),在日本横滨设立先进芯片封装研发中心,此举旨在强化其在该领域的技术实力,进一步挑战台积电的领先地位。

该研发中心选址横滨港未来区的Leaf Minato Mirai大楼,这栋总建筑面积达47,710平方米的12层建筑(含4层地下空间)将被改造为集研究实验室与中试生产线于一体的研发基地,预计2027年3月正式启用。

值得注意的是,这是三星近十年来在日本首次收购大型建筑,此前其2015年曾出售东京六本木总部大楼部分股份,此次布局凸显了对先进封装赛道的战略重视。

从合作生态来看,三星的横滨研发中心将重点深化与日本半导体产业的协同。计划与Disco Corp、Namics Corp、Rasonac Corp等日本材料和设备供应商建立技术合作,并加强与东京大学的产学研联动——该校距离研发中心不到一小时车程,三星计划从中招聘大量硕士和博士级研究人员,充实研发团队。横滨市也将为该项目提供25亿日元的启动补贴,为研发中心的落地提供支持。

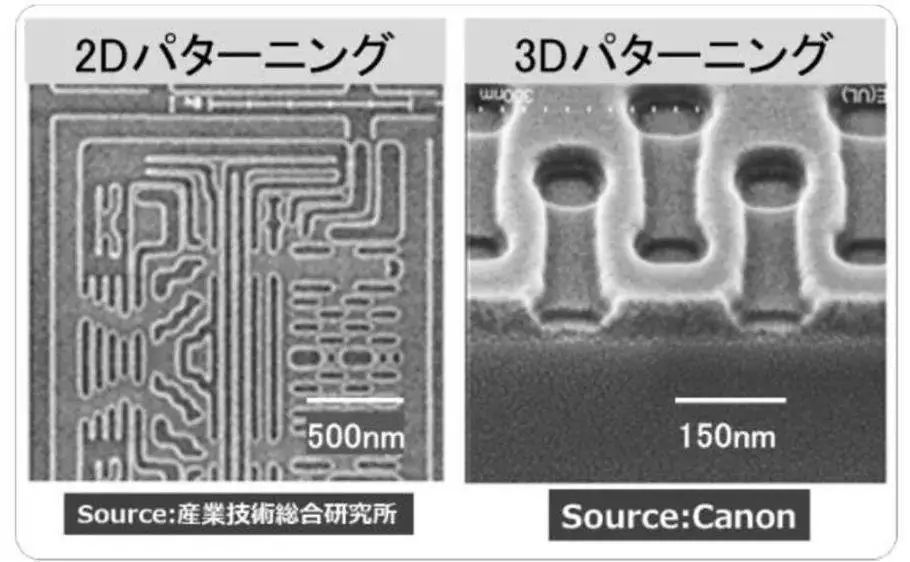

作为芯片性能提升的关键技术,先进封装通过2.5D/3D堆叠、Chiplet集成等方式,无需依赖超精细纳米制程即可增强芯片功能,在AI芯片制造中至关重要。但目前三星在该领域仍落后于台积电:Counterpoint数据显示,2025年第一季度台积电在代工、封装和测试市场的总份额达35.3%,而三星仅占5.9%,尤其在高端封装产能和技术上差距明显。

不过,市场增长潜力与自身突破为三星提供了动力。先进芯片封装市场规模预计将从2023年的345亿美元增长至2032年的800亿美元,而三星近期斩获特斯拉165亿美元AI6芯片订单,被业内视为其交钥匙服务(代工+封装一体化)能力提升的佐证。此次横滨研发中心的设立,正是三星完善“设计-制造-封装”全链条服务、追赶台积电的关键布局。

随着三星在横滨加码先进封装研发,全球半导体封装市场的竞争将进一步升级。这不仅是技术层面的较量,更是产业链生态的比拼,而横滨研发中心或将成为三星缩小与台积电差距的重要支点。

在先进封装技术的下一代竞争中,三星电子正全力推进“SoP(System on Panel,面板级系统)”技术的商业化落地,直接对标台积电的SoW(System-on-Wafer,晶圆级系统)技术和英特尔的EMIB工艺,争夺下一代数据中心级AI芯片的制高点。

三星SoP技术的核心创新在于采用415mm×510mm的超大尺寸长方形面板作为封装载体,这一尺寸远超传统12英寸晶圆(直径300mm)的有效利用面积。传统晶圆级封装受限于圆形晶圆形态,最大可集成的矩形模块尺寸约为210mm×210mm,而三星SoP面板可轻松容纳两个此类模块,甚至能生产240mm×240mm以上的超大型半导体模块,为超大规模AI芯片系统提供了更大的集成空间。

技术架构上,SoP省去了传统封装所需的印刷电路板(PCB)和硅中介层,通过精细铜重分布层(RDL)实现芯片间的直接通信。这种设计不仅提升了集成度,还能降低封装成本,尤其适配AI芯片和数据中心高性能计算场景的需求。三星在面板级封装领域积累的FOPLP技术经验,为SoP的研发提供了坚实基础。

商业化推进方面,三星将特斯拉第三代数据中心AI芯片系统视为重要目标。该系统计划集成多颗AI6芯片,初期拟采用英特尔EMIB技术生产。若三星能解决SoP面临的边缘翘曲、量产稳定性及高密度RDL工艺开发等难题,凭借更大封装面积和成本优势,有望进入特斯拉封装供应链。此外,三星同步研发的“3.3D”先进封装技术,将进一步提升其封装效率与成本竞争力。

此外,作为三星的主要竞争对手,台积电的SoW技术已进入实际应用阶段。该技术基于12英寸晶圆载体,通过InFO技术扩展而来,分为SoW-P(仅集成SoC组件)和SoW-X(集成SoC+HBM+I/O裸片)两个平台。其中SoW-P已投入生产,面向移动及边缘设备;SoW-X计划2027年投产,可集成16个高性能计算芯片和80个HBM4模块,专为AI/HPC场景设计,能提供高达260TB/s的die-to-die带宽。

台积电SoW技术依托成熟的晶圆制造体系,在良率控制和量产稳定性上具备优势,目前已被特斯拉、Cerebras等企业用于超级计算芯片量产。其最新发布的SoW-X技术,通过重构晶圆设计和先进液冷策略,可支持17000W功率预算,性能较传统计算集群提升46%,功耗降低17%。

三星押注SoP技术,本质上是通过差异化路径挑战台积电在先进封装领域的主导地位。对三星而言,SoP的成功商业化不仅能增强其“设计-制造-封装”一体化服务能力,更能巩固与特斯拉等大客户的合作——此前三星已斩获特斯拉165亿美元AI6芯片代工订单,若SoP技术成熟,有望将封装环节也纳入合作范围。

尽管目前SoP面临大规模作业稳定性等技术挑战,且超大型封装仍属利基市场,但三星正通过持续研发提升良率,试图在台积电SoW-X全面量产前抢占市场先机,重塑先进封装领域的竞争格局。

据最新消息显示,三星已明确计划在2028年将玻璃基板引入先进半导体封装领域,核心目标是用玻璃中介层取代传统硅中介层,这也是其玻璃基板技术路线图首次正式曝光。

中介层作为AI芯片2.5D封装结构的关键组件,承担着连接GPU与HBM内存的重要功能,直接影响芯片的数据传输效率。目前主流的硅中介层虽具备高速传输和高热导率优势,但材料成本高昂、制造工艺复杂,已成为制约AI芯片降本增效的瓶颈。而玻璃中介层凭借易实现超精细电路的特性,不仅能进一步提升半导体性能,还能显著降低生产成本,成为业界公认的替代方向。

三星的技术路线选择颇具策略性。为加快原型开发进度,其优先开发小于100×100毫米的玻璃单元,而非直接采用510×515毫米的大尺寸玻璃面板。尽管小尺寸可能影响量产效率,但能帮助三星更快完成技术验证并切入市场。

这一决策与AMD等企业的规划形成呼应——业界普遍预期2028年将成为玻璃中介层规模化应用的关键节点。

同时,在技术落地层面,三星充分发挥集团化作战优势。今年3月起,三星电子已联合三星电机、三星显示等关联企业共同研发玻璃基板技术:三星电机贡献半导体与基板结合的专有技术,三星显示则提供玻璃工艺支持,形成跨领域技术协同。近期技术人才的加盟,进一步强化了其在该领域的研发实力。

产线布局上,三星计划将外部合作企业提供的玻璃中介层,与天安园区现有的面板级封装(PLP)生产线结合进行封装作业。PLP技术作为在方形面板上完成封装的工艺,相比传统晶圆级封装(WLP)具有更高的生产效率,且与玻璃基板的方形特性高度适配,为玻璃中介层的量产提供了现成的制造基础。

三星此举直指AI时代的封装需求痛点。在去年的晶圆代工论坛上,三星已提出涵盖晶圆代工、HBM和先进封装的一站式AI解决方案战略,而玻璃基板技术的加入将进一步完善这一体系。通过引入玻璃中介层,三星既能提升封装环节的性能与成本优势,又能与自身的HBM内存、先进制程代工业务形成协同,增强对AI芯片客户的综合服务能力。

值得注意的是,三星的玻璃基板策略与行业对手形成差异化。其并未盲目追求大尺寸面板技术,而是通过小单元快速验证、集团资源协同、现有产线复用的组合策略,稳步推进技术落地。这一务实路径不仅降低了技术风险,更凸显了三星在先进封装领域“多点突破、持续迭代”的整体布局思路。随着2028年落地节点的临近,玻璃基板或将成为三星挑战封装技术制高点的又一重要筹码。

在移动AI技术快速发展的背景下,封装技术需在高性能、低功耗与紧凑设计之间找到精准平衡。三星的扇出型封装(Fan-Out PKG)技术凭借灵活架构与高效性能,成为移动AI芯片的关键支撑方案。

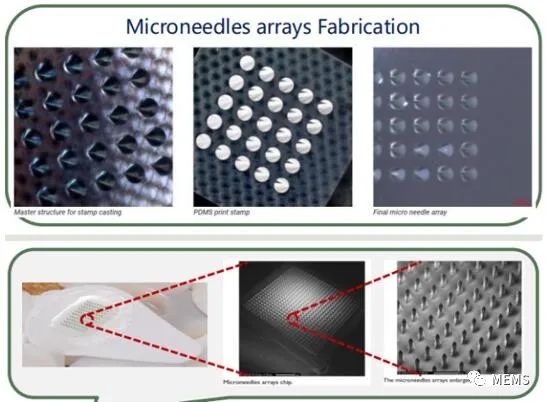

扇出型封装技术自2023年起已应用于移动 AP(应用处理器)量产,其核心采用芯片后装和双面重分布层(RDL)的FOWLP(扇出晶圆级封装)技术。

相比传统封装方案,该技术实现了多维度提升:工艺周转时间缩短33%,大幅提升生产效率;架构设计更具灵活性,可适配不同移动设备的定制化需求;热阻降低45%,显著增强散热能力,有效解决了移动设备紧凑空间内的散热难题。

针对移动AI对低功耗宽I/O内存的需求,三星进一步推出多芯片堆叠FOPKG技术。通过采用高纵横比铜柱(AR6:1)和精细间距RDL设计,该技术实现了I/O密度提升8倍、带宽提高2.6倍的性能飞跃,同时生产率较传统垂直引线倍,在提升性能的同时兼顾了量产经济性。

不过,扇出型封装在移动设备应用中仍面临独特挑战。移动设备对功耗和散热的高敏感性,要求技术在高密度互连中解决材料匹配问题——例如不同材料热膨胀系数(CTE)的不一致可能导致应力累积,影响封装可靠性。

此外,随着移动AI算力需求的持续增长,扇出型封装的扩展性仍需优化。对此,三星正通过材料创新(如研发低CTE基板)和模块化设计,进一步提升技术对多样化移动场景的适应性。

作为三星异构集成生态系统的重要组成部分,扇出型封装与HBM、3D逻辑堆叠、I-Cube等技术形成协同,共同推动移动AI芯片的性能突破。

未来,通过持续提升堆叠层数、优化间距设计和扩大中介层尺寸,三星扇出型封装技术有望在解决散热瓶颈、工艺复杂性和成本控制等挑战的过程中,继续引领移动AI封装领域的技术演进。

在先进封装技术的布局中,三星电子还推出了SAINT(三星先进互连技术)体系,聚焦存储与逻辑芯片的协同封装,通过创新3D堆叠技术构建差异化竞争力。

SAINT技术体系涵盖三种针对性的3D堆叠方案,分别适配不同芯片类型的集成需求:

SAINT-S:专为SRAM设计的堆叠技术,优化静态随机存取存储器的集成效率;

SAINT-D:针对HBM内存与逻辑芯片的协同设计,采用垂直堆叠架构,将HBM芯片直接堆叠在CPU或GPU等处理器顶部。

其中,SAINT-D技术最具创新性,彻底改变了传统2.5D封装中通过硅中介层水平连接HBM与GPU的模式。它采用热压键合(TCB)工艺实现HBM的12层垂直堆叠,成功消除了对硅中介层的依赖,不仅简化了结构,更带来显著性能提升:热阻较传统工艺降低35%,良率达到85%。

这一技术为HBM内存与逻辑芯片的高效协同奠定了基础,2025年三星凭借该技术已占据全球25%的HBM产能份额。不过,垂直堆叠方案也对HBM内存基片的制造工艺提出了更高要求,需要开发更复杂的基片生产技术。

为支撑SAINT技术的落地与量产,三星同步推进全球封装设施布局。在韩国本土,三星与忠清南道天安市签订协议,计划建设占地28万平方米的先进 HBM 封装工厂,预计2027年完工;在日本横滨,三星正在建设Advanced Packaging Lab(APL)研发中心,重点攻关下一代封装技术,聚焦HBM、人工智能和5G等高价值芯片应用的封装创新。

通过SAINT技术体系的构建,三星进一步强化了存储与逻辑芯片的协同封装能力,为AI、高性能计算等领域提供了更高效率、更低功耗的集成解决方案,也为其在先进封装赛道的竞争增添了关键筹码。

在先进封装技术的竞争格局中,三星电子构建了以I-Cube和X-Cube为核心的技术体系,分别覆盖2.5D和3D IC封装领域。通过与台积电、英特尔等对手的技术对比,可更清晰把握三星在该领域的定位与特色。

三星的I-Cube技术聚焦2.5D封装领域,细分为I-Cube S、I-Cube E以及衍生的H-Cube三种方案,通过不同的中介层设计满足多样化需求。

I-Cube S采用硅中介层(Silicon Interposer)作为核心连接载体,将逻辑芯片与高带宽存储器(HBM)裸片水平集成在同一中介层上,实现高算力、高带宽数据传输与低延迟特性。

其技术优势体现在三大方面:一是在大尺寸中介层下仍能保持出色的翘曲控制能力;二是具备超低信号损失和高存储密度特性;三是显著优化了热效率控制。从结构上看,I-Cube S与台积电的CoWoS-S技术相似,均采用“芯片-硅转接板-基板”的三层架构,适用于对性能要求严苛的高端AI芯片场景。

与I-Cube S的整体硅转接板不同,I-Cube E采用“嵌入式硅桥(Embedded Silicon Bridge)+RDL中介层”的混合架构:在高密度互连区域部署硅桥以实现精细布线,其余区域则通过无硅通孔(TSV)结构的RDL中介层完成连接。

这种设计既保留了硅桥的精细成像优势,又发挥了RDL中介层在大尺寸封装中的灵活性。该技术与台积电的CoWoS-L架构相近,均借鉴了英特尔EMIB技术的核心思路,在平衡性能与成本方面更具优势。

H-Cube是I-Cube系列的衍生技术,采用“硅中介层-ABF基板-HDI基板”的混合结构。通过将精细成像的ABF基板与高密度互连(HDI)基板结合,H-Cube可支持更大的封装尺寸,布线密度较基础版I-Cube S进一步提升。

不过从技术演进来看,H-Cube更偏向过渡性方案——随着HDI基板布线能力的提升,ABF基板的中间层未来可能被省略,因此三星未将其作为独立技术类别,而是归入I-Cube体系下。

X-Cube是三星面向3D IC封装的核心技术,通过硅通孔(TSV)实现芯片间的垂直电气连接,显著提升系统集成度。根据界面连接方式的不同,X-Cube分为两种类型:

X-Cube (bump):采用凸点(bump)连接上下芯片界面,技术成熟度高,适合对成本敏感的中高端应用。

X-Cube (Hybrid Bonding):采用混合键合技术实现界面连接,可大幅提升互连密度和热传导效率,是面向未来的高性能方案。

两种方案结构框架一致,核心差异在于连接精度与性能表现,共同构成三星在3D封装领域的技术储备。

整体而言,与台积电作为纯代工厂的技术输出模式不同,三星和英特尔的先进封装技术更多服务于自身芯片产品,因此市场知名度相对较低。

在技术路线上,三星目前更多扮演跟随者角色,I-Cube和X-Cube系列与台积电产品存在较多相似性。若想实现赶超,三星需在技术差异化和生态建设上加大投入。不过,先进封装作为半导体产业的“朝阳赛道”,技术成熟度仍有巨大提升空间,三星凭借其在存储芯片与晶圆制造领域的协同优势,未来有望在该领域实现突破。

在晶圆代工业务承压的背景下,三星将先进封装视为战略突围的核心方向,通过多维度布局构建竞争壁垒。

从70亿美元押注美国封装工厂抢占市场空白,到日本横滨研发中心深化技术协同;从推进SoP面板级封装挑战台积电SoW霸权;再到规划2028年玻璃基板技术落地,Fan-Out PKG支撑移动AI,SAINT体系强化存储与逻辑协同,以及I-Cube与X-Cube覆盖2.5D/3D封装场景,三星形成了“技术研发+产能落地+生态协同”的立体布局。

三星致力于通过差异化技术路径弥补先进制程短板,依托“设计-制造-封装”一体化能力争夺AI、数据中心等高端市场,同时借助美国政策红利与本土化供应链巩固客户合作。尽管面临成本高企、良率优化等挑战,但三星凭借集团资源协同与技术迭代韧性,正逐步缩小与头部玩家的差距。

展望未来,随着各项技术的成熟落地,三星有望在先进封装这一战略高地实现突破,重塑全球半导体产业的竞争格局。

*免责声明:本文由作者原创。文章内容系作者个人观点,半导体行业观察转载仅为了传达一种不同的观点,不代表半导体行业观察对该观点赞同或支持,如果有任何异议,欢迎联系半导体行业观察。

证券之星估值分析提示天安行业内竞争力的护城河较差,盈利能力良好,营收成长性一般,综合基本面各维度看,股价合理。更多

以上内容与证券之星立场无关。证券之星发布此内容的目的在于传播更多信息,证券之星对其观点、判断保持中立,不保证该内容(包括但不限于文字、数据及图表)全部或者部分内容的准确性、真实性、完整性、有效性、及时性、原创性等。相关内容不对各位读者构成任何投资建议,据此操作,风险自担。股市有风险,投资需谨慎。如对该内容存在异议,或发现违法及不良信息,请发送邮件至,我们将安排核实处理。如该文标记为算法生成,算法公示请见 网信算备240019号。

新闻资讯

-

又一巨头发力先进封装 08-17

-

纳米材料及纳米材料的制备方法简 08-17

-

先进制造技术(微纳制造)ppt 08-16

-

纳米技术有哪些发明 纳米技术一 08-16

-

恭喜!亘芯悦国产首台28纳米设 08-16

-

苹果iPhone 18突然曝光 08-16

-

原子级制造行业发展现状与产业链 08-16

-

速度跃升千倍成本骤降95%!港 08-16