咨询电话: 13704000378

三星电子突破DRAM技术壁垒 成功产出10纳米以下工作晶圆!

发布于 2026-04-26 01:06 阅读()

【CNMO科技消息】CNMO从韩媒获悉,三星电子在DRAM制造技术方面取得突破,首次成功产出10纳米以下级别的工作晶圆。这一进展标志着该公司在克服DRAM“10纳米魔咒”方面迈出了关键一步。

据业界消息,三星电子上月生产了采用10a工艺的晶圆,并在芯片特性检测过程中确认了工作晶圆的存在。这是该公司首次应用4F平方单元结构和垂直通道晶体管工艺的结果。在DRAM行业,10纳米级别工艺通常按1x、1y、1z、1a、1b、1c、1d的顺序划分代际。10a代表1d之后的下一代,是首个低于10纳米的节点。专家分析其实际电路线纳米水平。

工作晶圆是指从晶圆上切割下来的芯片中能够按设计正常运作的部分。在开发阶段产出工作晶圆,被视为设计与工艺方向正确的信号,之后将进行良率提升和可靠性验证等后续工作。三星电子计划今年完成基于此结构的10a DRAM开发,明年进行质量测试,并于2028年将其转移到量产生产线F平方和VCT结构,并从10d开始转向3D DRAM。

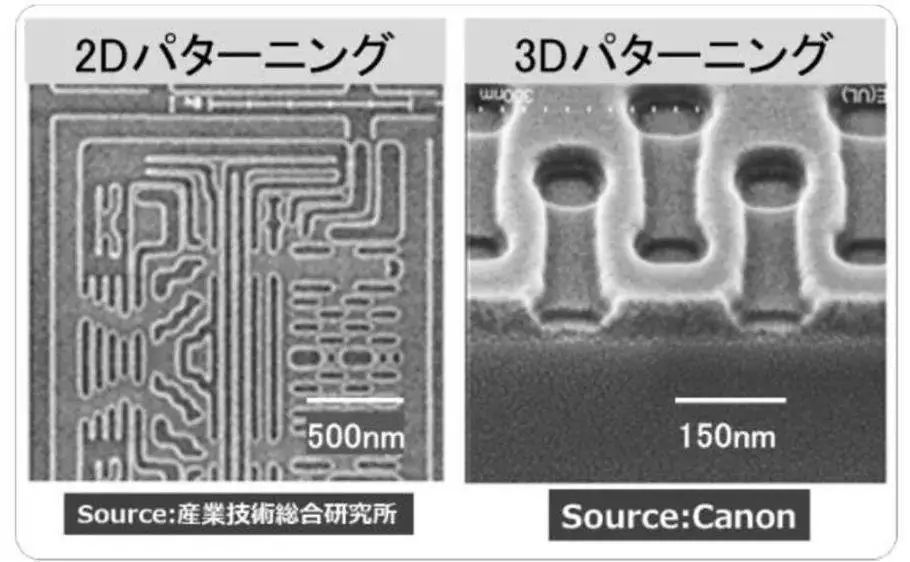

此次突破的关键在于采用了4F平方单元面积和垂直通道晶体管这两项新技术。此前DRAM单元面积为6F平方,而10a工艺将其缩小至4F平方。理论表明,在相同的芯片尺寸下,转向4F平方结构可容纳30%至50%更多的单元,有利于提升容量、速度并降低功耗。为了在缩小后的单元面积上布置栅极、通道和电容器,三星引入了VCT技术。该技术将电容器置于晶体管上方,改变了以往两者各自占用单元面积的传统布局。

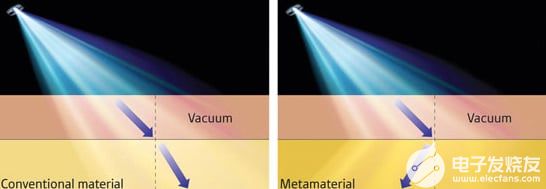

随着4F平方和VCT技术的应用,核心材料也随之改变。三星电子将通道材料从硅改为铟镓锌氧化物,以在缩小单元中抑制泄漏电流并确保数据保持特性。此外,在单元周围布局的各种外围电路将采用单独晶圆加工,并通过晶圆对晶圆混合键合技术连接的PUC方案。

业界人士指出,三星电子此次成功产出工作晶圆,意味着采用该技术的开发与量产工作将加速推进。与此同时,其他厂商的策略有所不同。美光计划尽可能维持现有设计。中国DRAM厂商由于无法进口极紫外光刻设备,在现状下难以进行线宽缩小,因此正积极开发3D DRAM,认为一旦DRAM实现3D化,便可使用传统光刻设备制造先进产品。SK海力士则计划在10b节点而非10a节点应用4F平方和VCT技术。

特别声明:以上内容(如有图片或视频亦包括在内)为自媒体平台“网易号”用户上传并发布,本平台仅提供信息存储服务。

五代十国,深挖这段被教科书删除的53年,血腥到不敢拍成电视剧

今日热点:爱奇艺回应暂停页面广告争议;经纪公司否认THEBOYZ解约成功……

iPhone18 Pro Max模型机曝光:厚了、重了、摄像头凸起更大了!

索尼最强旗舰!Xperia 1 VIII外观新鲜出炉:无刘海无挖孔 背部撞脸一加

新闻资讯

-

三星电子突破DRAM技术壁垒 04-26

-

重磅官宣!12nm 制程正式落 04-26

-

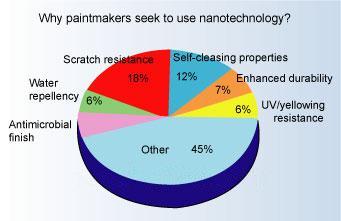

南京理工大学纳米材料与技术(本 04-24

-

欧洲芯片巨头官宣:我已经在中国 04-24

-

这家EDA公司“杀回”上海悄悄 04-24

-

中国光学超材料取得新突破 为多 04-24

-

改变世界的新印刷术!中国科学家 04-23

-

华升纳米CCMT2026再创里 04-23