咨询电话: 13704000378

日本公司大幅降低芯片制造成本!

发布于 2025-12-10 16:58 阅读()

据《日经新闻》报道,日本大日本印刷株式会社(DNP)开发出一种技术,有望将先进半导体的制造能耗降低 90%,这一举措有望大幅降低人工智能芯片的制造成本。

大日本印刷株式会社计划于 2027 年开始批量生产一种模板材料,该材料k8凯发官网入口可用于使用佳能芯片制造设备制造尖端的 1.4 纳米芯片。

制造此类尖端芯片现在需要极紫外(EUV)光刻设备,而这种设备目前只有荷兰公司ASML Holding生产。在晶圆上形成电路的光刻工艺占芯片制造总成本的30%到50%。

电路尺寸越小,需要使用的紫外光次数就越多,从而导致功耗增加。EUV光刻设备单价高达数亿美元,这进一步加重了芯片制造商面临的沉重投资负担。

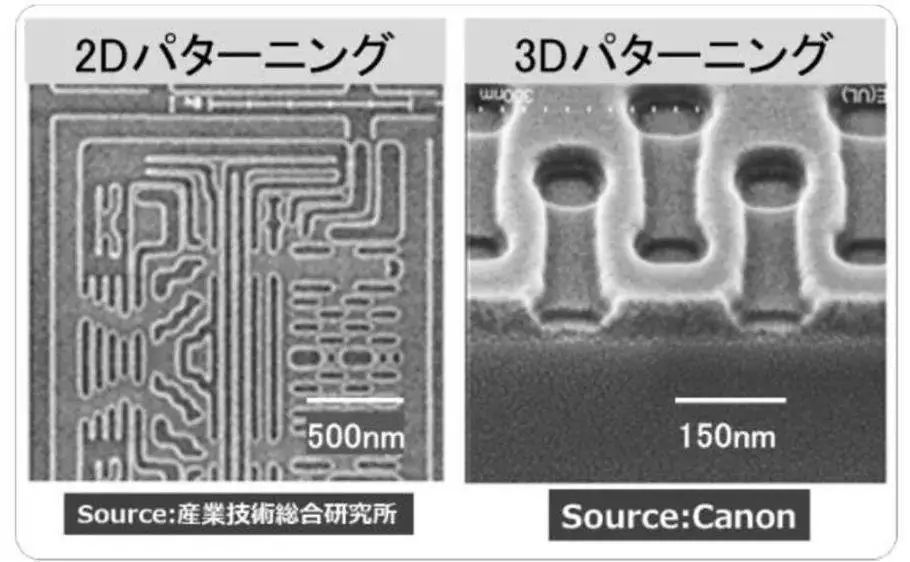

日本佳能公司生产半导体光刻机,该公司还拥有纳米压印芯片制造设备,该设备通过将电路压印到晶圆上来制造电路。

人们一直认为纳米压印工艺与 2 纳米及更先进的芯片不兼容,但 DNP 开发了一种电路模板,可与制造 1.4 纳米芯片的设备一起使用。

佳能于 2023 年开始销售纳米压印设备,该设备比 EUV 光刻设备耗电量更低。单价估计为数十亿日元(10 亿日元约合 640 万美元),远低于 EUV 光刻的成本。

由于模板与晶圆直接接触以形成电路,杂质的存在很容易导致缺陷。提高速度也是一项挑战。一些公司,例如存储芯片制造商铠侠控股,已经引入纳米压印设备用于测试,但尚未有任何公司将其应用于大规模生产线。

下一代1.4纳米芯片将应用于人工智能数据中心和自动驾驶系统。韩国三星电子和台积电计划分别于2027年和2028年开始量产。

两家公司似乎都对纳米压印光刻技术感兴趣,但它们的工厂都是按照光刻设备设计的,这给生产方式的转变设置了很高的障碍。纳米压印设备必须具备令人信服的经济效益才能得到广泛应用。

佳能和尼康曾经主导着全球光刻设备市场。但ASML赢得了小型化竞赛,现在占据了90%的市场份额。

如果纳米压印市场未来扩张,可能会为像DNP这样的材料制造商创造机遇。富士胶片控股公司已宣布计划进军该市场,生产用于电路形成过程中晶圆上的材料。

佳能于 2024 年向德克萨斯电子研究所(一家包括德克萨斯州和英特尔等半导体公司的公私合营组织)交付了其首台纳米压印光刻设备。

新闻资讯

-

日本公司大幅降低芯片制造成本 12-10

-

Imec成功采用EUV光刻技术 12-10

-

加快发展新质生产力 打造江阴“ 12-10

-

华为申请基于纳米片的器件的制造 12-10

-

纳米技术简介用途与发展前景? 12-09

-

日经亚洲:中国可能成为荷兰和日 12-09

-

精密仪器行业现状与发展趋势分析 12-09

-

破局与共生:中麒光电双技术路线 12-09